×

ip 就其本质来讲是一个能提供正确接口信号的功能模块。随着eda 技术和半导体工艺技术的发展,集成电路的规模越来越大,设计越来越复杂,使用ip 核是一个必然趋势。研究开发超大规模集成电路设计业亟需的、具有良好应用前景的ip 核,积极推动ip 核的应用,对于我国集成电路产业的良性发展将会起到极大的促进作用。usb 通用串行总线是众多计算机厂商和电信厂商共同开发的用于计算机外设连通到计算机的规范。它日益成为一种主流的计算机接口标准。它包含3 大技术要素:主机,集线器和功能。国外一些公司近年来相继开发出基于上述3 个技术要素的ip,国内一些ic 设计公司也开始在这些领域内作研究,但由于usb 主机控制器ip的设计一直是usb 系统设计中的难点,成果较少。

遵循usb 规范和开放主机总线接口(open hostcontroller interface, ohci)规范,基于asic流程开发出了usb1.1 ohci 主机控制器ip。

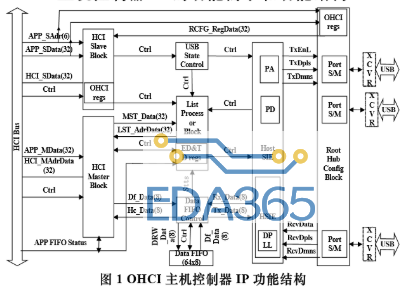

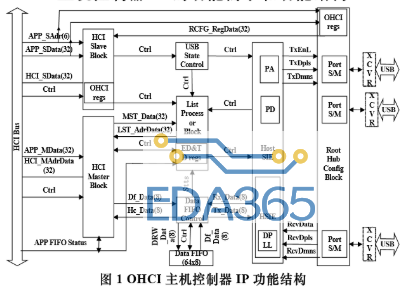

在所有的实现中,主机控制器都必须提供基本相同的功能,主要包含状态处理、串行化与反串行化、帧产生、数据处理、协议引擎、传输差错控制、远程唤醒、集线器、主机系统接口。根据这些要求,参考usb 规范和ohci 规范,通过定义一组与主机系统存储器交互的虚拟主机总线接口以及收发器接口,作者将设计分成若干部分,将每一部分需要完成的目标功能单独描述并验证,在此基础上再作顶层的整合。进行功能划分后ohci 主机控制器ip 的结构如图1。

主机控制器功能模块设计

主机系统接口模块

该模块由两个部分组成,主要功能是在主机系统与ohci主机控制器之间建立高速的数据通道。按照数据传输的发起者不同,可以分为hci 主模块和hci 从模块,前者负责发起对系统存储器的读写操作,后者负责响应主机系统或cpu 的读写操作。针对不同的soc(system on a chip)片内总线,可以在主机系统接口模块与片内总线之间实现简单的胶合逻辑,从而实现usb 主机控制器ip 的重复使用。

状态控制模块(usb state control)

它是列表处理器层次结构的上层模块,直接由ohci 寄存器来控制。它实现了主状态机,可用来触发列表处理器中较低层次的状态机。主状态机还可以生成一些控制信号,以便控制下列操作:传输sof(start of frame)标示、复位/恢复、向系统存储器中的hcca(host controller communicationarea)写回每微秒的帧序号等。该模块还实现了优先级算法,该算法基于ohci 寄存器决定当前需要处理周期性列表还是非周期性列表,如果非周期性列表获得优先权,它可以确定当前应该执行的传输是控制传输还是批传输。

列表处理器模块

它是整个ip 核最关键的控制器,实现了ohci 规范规定的绝大部分协议。按照ohci 规范,它有多个状态机实现列表服务流、列表优先级、ed/td 服务、状态写回、td 撤退等功能。它充当一个控制器,连接hci master 和host sie,帮助它们在系统存储器和usb 之间实现数据传输。它包含4个子模块:列表服务流程模块、端点描述符服务流程模块、传输描述符服务流程模块以及hci master 接口模块。

数据fifo 和数据fifo 控制模块

数据fifo 模块实现了一个宽度为8bit、深度为64byte的fifo,它的主要作用是同步host sie 和hci master 之间的数据传输。数据fifo 控制模块实现了主机控制器的内部数据fifo 的方向控制逻辑,以便在usb 和系统存储器间传输数据。

对于in packet,当数据从端点接收时,host sie 将其存储在数据fifo 中。当所有数据收到(对gtd/itd 而言)或数据fifo 中的数据超过一定的门限(≥16byte),td 状态机发起一个写命令通知hci master 接口模块。hci master 接口模块提供写的起始地址,同时本模块提供写回的字节数,触发hci master 执行一个写周期。hci master 写操作结束以后,它将控制返回到tdsf 的td 状态机。

类似的,对于out packet,td 状态机通知本模块从系统存储器读取数据。读操作的地址和字节数由hci master 模块来提供。若数据超过16byte,它将通过hci master 执行多次操作。

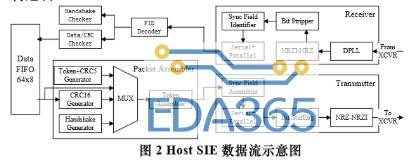

主机控制器串行接口引擎模块

本模块主要用来完成usb 规范中协议处理部分的功能。它用作主机控制器的协议引擎,并且与列表处理器、数据fifo 以及ohci 寄存器相连接,此外它还实现了用来同步hsie 和端口状态机之间接口的控制逻辑。本模块的数据流框图如图2 所示, 图中hsie 模块工作在48mhz、打包模块和拆包模块工作在12mhz,因此需要异步逻辑在不同的时钟域之间实现同步,为简单起见,图中省去了异步逻辑模块和控制逻辑。

在usb 数据接收期间,d 和d-信号经由差分接收器变成单端字位流,然后经由dpll 模块提取时钟和数据信息。在hsie 的接收器中实现了大部分协议解释功能, 诸如nrzi-nrz 的转变、位填充拆除、同步域检测、se0 检测、crc16 计算、超时逻辑、串并转换、速度控制等。在拆包模块中还实现了状态机来检测usb 的功能是否收到有效的握手信号。

在usb 数据发送期间,打包模块根据列表处理器的要求确定需要发送的包类型。有3 种类型的包:标示,数据,握手包。如果是数据包,则需要进行crc16 校验;如果是标示包,则需要进行crc5 校验;握手包不需要进行crc 校验。打包模块随后将字节流传送给hsie 的发送器进行同步域添加、并串转换、位填充、nrz-nrzi 转换等工作。限于篇幅,仅介绍其中的关键模块:时钟恢复和数据提取电路以及并行crc 算法。

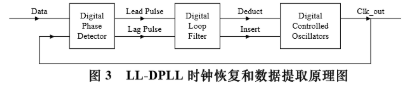

(1) 数字锁相环(digital phase lock loop,dpll)

由于usb 主机与usb 设备所采用的工作时钟完全分离性,唯一的交互信息是usb 总线上的字位流,为了正确提取字位流中包含的数据信息,必须有一套机制从接收到的字位流中恢复时钟信息。本文采用一种超前滞后型数字锁相环(lead lag dpll)来实现上述功能。ll-dpll 时钟恢复环路的原理如图3。

环路的工作原理如下: 数字鉴相器( digital phasedetector)比较字位流数据data 与本地跟随时钟clk_out 的相位,给出相位误差信号lead pulse 和lag pulse。数字环路滤波器对相对误差进行平滑滤波,并生成控制数控振荡器的控制信号deduct 和insert。dco 根据控制信号给出的指令,利用内部高速振荡器的产生的时钟调整输出时钟clk_out 的相位,使其跟随输入数据data 的相位。按照恢复时钟对输入的字位流进行采样,即可提取数据。

(2)并行crc 算法

为了提高串行数据的校验速率,在传统的串行crc基础上,本文提出了一种并行crc 算法,以crc5 为例,该算法的verilog 硬件描述如下:

module usbh_crc5(ci, d, co);

input [4:0] ci; //上一次输入数据crc 校验值或crc 初值

input [10:0] d;//输入的待校验数据

output [4:0] co;//本次输入数据的crc 校验输出

assign co[0] = d[10]^d[9]^d[6]^d[5]^d[3]^d[0]^ci[0]^ci[3]^ci[4];

assign co[1] = d[10]^d[7]^d[6]^d[4]^d[1]^ci[0]^ci[1]^ci[4];

assign co[2] = d[10]^d[9]^d[8]^d[7]^d[6]^d[3]^d[2]^d[0]^ci[0]^ci[1]^ci[2]^ci[3]^ci[4];

assign co[3] = d[10]^d[9]^d[8]^d[7]^d[4]^d[3]^d[1]^ci[1]^ci[2]^ci[3] ^ci[4];

assign co[4] = d[10]^d[9]^d[8]^d[5]^d[4]^d[2]^ci[2]^ci[3]^ci[4];

endmodule

根集线器配置模块

本模块实现了针对根集线器部分的ohci 寄存器堆,并为每个下行端口实现了一个状态机以控制端口功能状态。根集线器配置模块可以根据不同的用户需求做到端口数目可配置,最多可配置15 个下行端口,为用户提供了很大的灵活性。

仿真与验证

usb 是一个复杂的系统,包括上层应用程序、usb 类驱动程序、主机控制器驱动程序、主机控制器以及usb 设备,为了对usb 主机控制器进行全面的行为级验证,必须建立相对完整的虚拟验证平台。本文的验证工作基于中科院计算所自行开发的soc 虚拟验证平台,主要验证下述内容:

(1)主机控制器ip 的ohci 寄存器堆的可编程性;

(2)主机控制器ip 与虚拟存储器之间数据传输的正确性;

(3)主机控制器ip 内部协议处理部分在不同种类传输情况下的正确性,包括帧管理、主状态机在各种条件下的状态转换和管理、串行化与反串行化、位填充与位填充拆除、时钟和数据信号提取、nrz 和nrzi 码相互转化、中断处理等;

(4)传输差错处理,包括crc 校验错、pid 校验错、位填充错、传输顺序错、应用程序缓冲区bufferoverrun 和bufferunderrun错、控制器内部数据fifo dataoverrun 和dataunderrun 错、设备babble、设备超时错等;

(5)根集线器配置部分功能,主要包括下行端口状态转换、设备连接/断开检测、端口过流检测、远程唤醒、设备挂起、usb 总线复位等。主机控制器ip 设计使用的硬件描述语言是verilog。仿真工具使用cadence 公司的ncsim。逻辑综合使用synopsys公司的design compiler。作者在rtl 设计完成以后在行为级作仿真。在确定行为正确以后,利用综合工具作逻辑综合,形成网表文件和综合后的时延估计(standard delay format,sdf)文件,然后利用这两个文件作门级仿真。

为简单起见,本文列出综合后门级仿真一个典型setup交易的波形图,如图4 所示。图中usb 总线上进行的交易为usb 总线复位结束以后,主机控制器检测到根端口1 上接入了一个usb 设备,由根端口作完设备速度评估,判断出接入端口1 的虚拟设备为全速设备,然后应用程序根据这些信息以及现有系统中usb 设备的相关信息来设置当前接入的设备地址,图中所示波形展示了主机发出setaddress 请求以后usb 总线上的数据线d 和d-的行为以及主机控制器ip 的端口数据线的行为。

结论

usb 主机控制器ip 设计是一个综合考虑软硬件系统各方面情况的复杂设计,工作时没有经验可以参考,所以也遇到不少问题。在ip 设计中,基本是按照ip 必须遵从的两个规范来划分电路的功能子模块,然后在子模块中具体实现相关的功能,自顶向下设计。在行为级和综合后的门级仿真时,采用虚拟的软硬件协同验证方法,模拟现实操作系统中针对当前有待验证的电路将会发生的行为,进行高强度的测试和验证,电路工作正常。这些结果说明软硬件协同设计和验证在ip 设计过程当中也是适用的,本设计也是这方面工作的一个探索。

『本文转载自网络,皇冠最新app版本的版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多